零基础入门学习什么编程语言比较好如果你想学习编程,虽然选择第一门编程语言与你想用它来做什么最终达到什么目的有很大的关系,但是事实上某些编程语言的确比其他语言要好学。

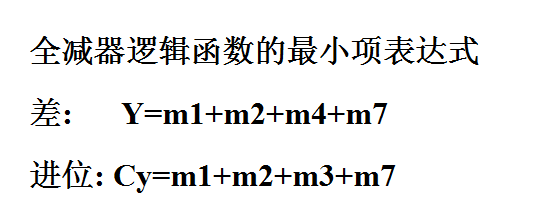

全减器逻辑表达式推导

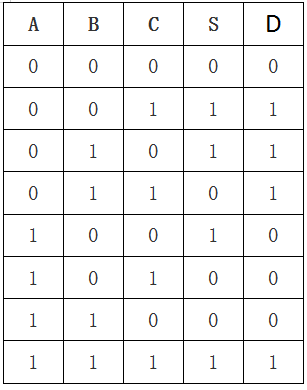

全减器的真值表和逻辑表达式

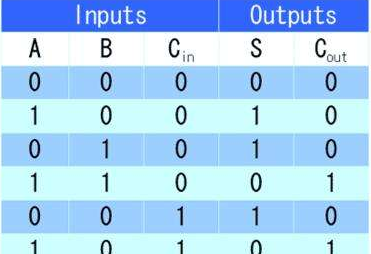

全减器真值表如下:其中A表示被减数,B表示减数,S表示本位最终运算结果,即就是低位向本位借位最终结果,C表示低位是否向本位借位,D表示本位是否向高位借位。

74ls138全减器逻辑表达式和电路图怎么写

4ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V。

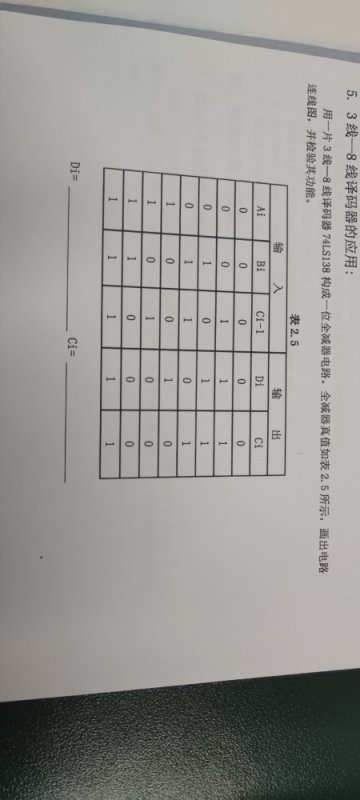

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

CO---向高位的借位 Y---两位数之差C1---来自低位的借位

真值表如下:其中A2=A0;A1=A1;A0=C1

故:Y=m1+m2+m4+m7;CO=m3+m5+m6+m7

【摘要】

74ls138全减器逻辑表达式和电路图怎么写【提问】

亲~这道题由我来回答,打字需要一点时间,还请您耐心等待一下。咨询结束的时候还请您给个赞[作揖]【回答】

您好【回答】

首先得弄清楚全加器的原理,你这里说的应该是设计1位的全加器。

全加器有3个输入端:a,b,ci;有2个输出端:s,co.

与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7)。

这里可以把3-8译码器的3个数据输入端当做全加器的3个输入端,即3-8译码器的输入A、B、C分别对应全加器的输入a,b,ci;将3-8译码器的3个使能端都置为有效电平,保持正常工作;这里关键的就是处理3-8译码的8个输出端与全加器的2个输出的关系。

现在写出全加器和3-8译码器的综合真值表:

(A/a,B/b,C/ci为全加器和译码器的输入,OUT为译码器的输出(0-7),s为加法器的和,co为加法器的进位输出)PS:假定译码器的输出为高电平有效。【回答】

A/a

B/b

C/ci

OUT

s

co

0

0

0

0

0

0

0

0

1

1

1

0

0

1

0

2

1

0

0

1

1

3

0

1

1

0

0

4

1

0

1

0

1

5

0

1

1

1

0

6

0

1

1

1

1

7

1

1【回答】

根据上面的真值表,可以设计出电路图:

将3-8译码器的输出OUT(1、2、4、7)作为一个4输入的或门的输入,或门的输出作为加法器的和;将3-8译码器的输出OUT(3、5、6、7)作为一个4输入的或门的输入,或门的输出作为加法器的进位输出。即完成了加法器的设计。

回过头来分析:

当加法器的输入分别为:a=1,b=0,ci=1时,对应3-8译码器的输入为A=1,B=0,C=1,这是译码器对应的输出为OUT(5)=1,其余的为0,根据上面设计的连接关系,s=0,co=1,满足全加器的功能,举其他的例子也一样,所以,设计全加器的设计正确。【回答】

我是问的全减器不是全加器谢谢【提问】

【提问】

【提问】

【提问】

【提问】

稍等【回答】

Y=m1+m2+m4+m7;CO=m3+m5+m6+m7【回答】

74ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V。用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号【回答】

还是不懂能不能直接把我发的图片这道题目的答案告诉我【提问】

还是不懂能不能直接把我发的图片这道题目的答案告诉我【提问】

还是不懂能不能直接把我发的图片这道题目的答案告诉我【提问】

还是不懂能不能直接把我发的图片这道题目的答案告诉我【提问】

4ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V。

用3线—8线译码器74LS138和门电路设计1位二进制全减器,输入为被减数、减数和来自低位的借位;输出为两数之差和向高位的借位信号。

CO---向高位的借位 Y---两位数之差C1---来自低位的借位

真值表如下:其中A2=A0;A1=A1;A0=C1

故:Y=m1+m2+m4+m7;CO=m3+m5+m6+m7

【回答】

di=m1+m2+m4+m7;ci=m3+m5+m6+m7【回答】

咨询结束的时候还请您给个赞[作揖]【回答】

如何看懂二进制全减器真值表?

刚开始看百度百科对全减器的介绍时心里也是一直mmp,不过搞懂了后,觉得百度百科的讲解还是挺准确的。下面是百度百科对全减器的真值表的介绍:

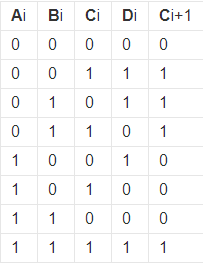

“Ai表示被减数,Bi表示减数,Di表示本位最终运算结果,即就是低位向本位借位最终结果,Ci表示低位是否向本位借位,C(i+1)表示本位是否向高位借位。(C(i+1)中的i+1是下标···)”

刚开始为什么看不懂呢?因为被一大堆诸如“本位”,“借位”,“低位向本位借位”,“本位向高位借位”这样的纸老虎吓到了。那接下来就对这些逐一分析。

首先明确,输入的是Ai、Bi和Ci。输出的是Di和C(i+1)。

因为我们都对十进制的减法比较熟悉,那么我们就以十进制减法为例来解释什么是“本位”,“借位”等等概念。

比如你我都清楚30-11=19,30是被减数,11是减数。但是我们按照小学刚学加减法时候的步骤一步一步来:

画图:

30 30 30

- 11 - 11 - 11

—— => —— => ——

= = 9 =19

图1 图2 图3

首先个位相减:0-1,不够减,所以个位的0需要向十位的3借一位,即“本位向高位借位”,然后再相减,即10-1=9,这样得到图2。

然后十位相减:3-1,但是由于刚刚个位相减时向3借了一位,即“低位向本位借位”,这样就变成了2-1=1,即“本位最终运算结果”。也就得到30-11最终结果如图3所示。

这样再看真值表或许可以明白些。

比如拿真值表的最后一行举例:

Ai=1,Bi=1,本来应该是Ai-Bi=1-1=0,但是别忘了Ci=1,也就是低位向Ai借了一位。

所以这时Ai-Bi=0-1,但是又不够减了,怎么办呢,所以Ai就需要向高位借位了,即本位向高位借位,也就得到了C(i+1)=1。

借位过后再减,也就得到了最终结果也就是Di,等于1。

其他的情况类似。

刚开始觉得这样设计好复杂,不过后来觉得一点也不复杂,反而是最简化的设计,就像全加器一样,许许多多个这样的器件组合在一起便可以完成大数的加减运算!

一位二进制全减器真值表怎么得到啊,死活看不懂啊,哪位好心的大神帮帮忙啊,我智商低,麻烦详细点!

最简单的全减器是采用本位结果和借位来显示,二进制中是借一当二,所以可以使用两个输出变量的高低电平变化来实现减法运算。

同时,全减器可以采用74LS138三线—八线译码器实现。全减器真值表如下:其中Ai表示被减数,Bi表示减数,Di表示本位最终运算结果,即就是低位向本位借位最终结果,Ci表示低位是否向本位借位,Ci+1表示本位是否向高位借位。

扩展资料:

真值表被用来计算真值泛函表达式的值(就是说是一个判定过程)。真值泛函表达式要么是原子(就是说是命题变量(或占位符)或命题函数 - 比如 Px)或建造自使用逻辑运算符(就是说 ∧ (AND),∨ (OR),¬ (NOT) - 例如 Fx & Gx)的原子公式。

真值表中的列标题展示了 (i) 命题函数与/或变量,和 (ii) 建造自这些命题函数或变量和运算符的真值泛函表达式。行展示对 (i) 和 (ii) 的 T 或 F 指派的每个可能的求值。换句话说,每行都是对 (i) 和 (ii) 的不同解释。

参考资料来源:百度百科-真值表

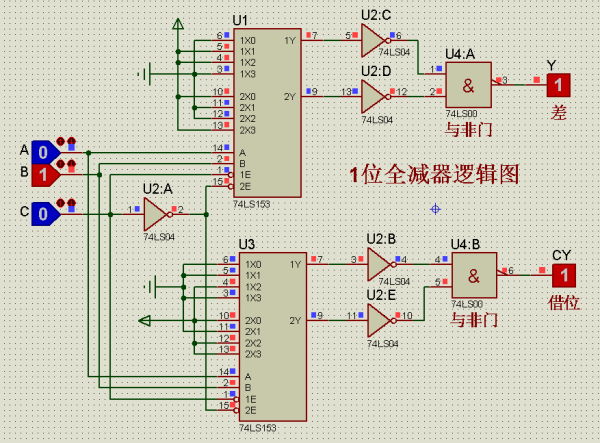

用双四选一数据选择器74HC153实现一位全减器,写出真值表,逻辑表达式,画出电路图

用双四选一数据选择器74HC153实现一位全减器,真值表如下

逻辑表达式如下

逻辑图

相关文章

- 详细阅读

-

linkboy 的“元素”里面的“cx编程详细阅读

欧姆龙的cx-one cx-p CXP730_SCHI 都是什么软件有什么用?cx-one当中包含了CX-Programmer(PLC编程)软件,还有CX-Simular(仿真),CX-Designer(HMI编程);LOGO语言有什么用以下内容来自