猿编程下载了用不了什么原因猿编程无法使用的原因可能有多种,下面列举了一些常见的原因和解决方法:

1. 网络连接问题:确保你的设备连接到了稳定的网络,尝试使用其他应用或者网页

verilog程序

每个Verilog HDL程序包括哪4个主要部分

每个Verilog程序包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

1、系统级(system):用高级语言结构实现设计模块的外部性能的模型。

2、算法级(algorithm):用高级语言结构实现设计算法的模型。

3、RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

4、门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

5、开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

扩展资料

一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。Verilog HDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL级的模型设计。

Verilog的设计初衷是成为一种基本语法与C语言相近的硬件描述语言。这是因为C语言在Verilog设计之初,已经在许多领域得到广泛应用,C语言的许多语言要素已经被许多人习惯。一种与C语言相似的硬件描述语言,可以让电路设计人员更容易学习和接受。

不过,Verilog与C语言还是存在许多差别。另外,作为一种与普通计算机编程语言不同的硬件描述语言,它还具有一些独特的语言要素,例如向量形式的线网和寄存器、过程中的非阻塞赋值等。总的来说,具备C语言的设计人员将能够很快掌握Verilog硬件描述语言。

参考资料来源:

百度百科——Verilog HDL

简单verilog程序解释下

if (B[i]) R = R + (A << (i-1));因为(A << (i-1))结果是与R做"+"的操作,所以(A << (i-1))结果的位数会自动扩展,这样就不是4位而是与R的位数相同8位,这样就不存在高位丢失了。verilog 程序,什么意思啊,尤其是这个<<

<<和>>是移位运算符,x<请问这个Verilog程序的功能是怎样的呢?

初步判断,这个模块会根据输入的B,在每个时钟的上升沿,往结果Q输出Bx75,我想作者可能本身的想法是往原先结果加上Bx75,但是他把TOUT = 32'b0写在了always块了,所以每次clk上升沿,TOUT都会清零。 很明显,这段代码的作者对于电路不了解,对于电路时序关系也不关心,完全是按照一个软件的写法在写Verilog代码,所以才会在always块中定义变量(看看always块开头,是不是很像C代码里,函数开头的变量定义和赋初值)、在always块中使用阻塞赋值并与非阻塞赋值混用。 那段for循环也是写的太复杂,用一个左移操作就可以完成的事情,for循环的电路开销是很大的,因为它实际上用Verilog编一个计数器的程序

举个简单点的例子,如下。

设计一个4bit的计数器,在记到最大值时输出一个信号

module counter_16 ( input clk, input rst_n, input cnt_in ,output reg cnt_out );

reg [3:0] cnt;

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) cnt <= 4'b0;

else if (cnt_in) cnt <= cnt +1'b1;

else cnt <= cnt;

end

always @ (posedge clk or negedge rst_n) begin

if (~rst_n) cnt_out <= 1'b0;

else if (cnt_in && cnt == 4'b1111) cnt_out <= 1'b1;

else cnt_out <= 1'b0;

end

endmodule

这实际上设计了一个16进制计数器其中的一位,你可以例化多个相同模块,将低位的cnt_out连接到高位的cnt_in,级联成一个任意位数的16进制计数器。

相关文章

-

猿编程的巩固挑战闪退是什么原因详细阅读

-

自学编程有什么渠道可以获取资料?详细阅读

在哪些网站可以自学编程?自学编程是不是很难精进呢?像B站等,包括一些视频软件上都是有这样的课程,自学编程的更多的是要实战练习一下。现在资源的共享性是非常的好的,很多的网站

-

CIE编程一级有什么用详细阅读

aice考级一级有用吗有用。

aice考级有助于提高学生的信息素养,aice考级一级也是实力的证明,当然是有用的。

aice考级为推进人工智能时代新型人才的培养、全面提升青少年人工智 - 详细阅读

-

超级计算机,大型机,小型机和微型计详细阅读

大中型计算机与小型、微型计算机之间的联系联系:单片计算机则只由一片集成电路制成,其体积小,重量轻,结构十分简单,性能介于巨型机和单片机之间的就是大型机、中型机、小型机和微

-

不懂编程可以做我的世界开发者吗详细阅读

我以后想在游戏公司开发游戏,但是完全不懂编程,可以吗?我觉得可以,有时候一些好的想法是许多做游戏的专业人员所不具备的,大家都只是跟风,看到有什么游戏就借鉴别人的做。程序员好

-

Win32编程时操作系统先发来WM_GETM详细阅读

CreateWindow是创建好空白窗口之后再发送WM_CREATE消息吗?WM_CREATE是最后一个消息之前有这些: 1.先发送 WM_GETMINMAXINFO=$0024: 此消息发送给窗口当它将要改变大小或位置

-

jiva编程输入任意三组整数输出三组详细阅读

java编程: 从键盘输入一个整数,如果输入的不是整数,则提示输入有误,请重新输入,直到输入正确为止。importjava.util.Scanner;

publicclassTest{

publicstaticvoidmain(String[] -

为什么在使用数组编程时,off-by-on详细阅读

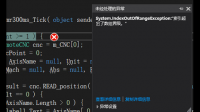

off-by-one错误大小差一。。就是指某个变量的最大值和最小值可能会和正常值差1,或者循环多执行一次/少执行一次。一般在临界情况时发生。为什么在使用数组的时候会发生错误?索

-

这面是一家新开的编程培训机构,有没详细阅读

一个刚办的教育培训机构,怎么可以快速招生?我认为招生主要的两个方向,一个是宣传招生。另一个就是转介绍了。对于我们学校来说,转介绍的来源占比更重,起码占到了60%。 1.服务好家